## **Z8038 FIO**

### **LH8038**

# Input/Output Interface Unit

#### **Features**

- Asynchronous bidirectional FIFO buffer, used with most major microprocessors as CPU/CPU or CPU/peripheral interface.

- Interlocked of IEEE-488 handshake port mode; Empty, Full, and Wait/Request lines for high-speed data transfer.

- 128 x 8 organization, expandable to 16 bits wide; cascadable to any depth.

- Pattern recognition logic stops DMA transfer and/or interrupts CPU.

- Preset byte count in FIO buffer can interrupt CPU.

- All registers read/write and directly addressable.

#### Description

The Z-FIO is a general-purpose microprocessor interface that provides elastic buffering between asynchronous CPUs in a parallelprocessor network or between CPU and peripheral circuits. The Z-FIO can interface a Z-bus microprocessor or any other major processor to another microprocessor or to a peripheral circuit or port.

In Z8000 systems, the FIO furthers distributed-processor operation because it can interconnect components or subsystems operating at different speeds. Also, it can increase system throughput by transferring words as well as bytes. This bidirectional device accepts data and holds it until it can be used by another device in the system. In most I/O transactions, introducing a 128-deep buffer cuts interrupt servicing overhead by two orders of magnitude.

The Z-FIO greatly facilitates system throughput by moving variable-size blocks under either direct memory access or interrupt control—an especially important consideration when fast peripheral circuits need interfacing. Complete status information is also provided for operation in polled environments.

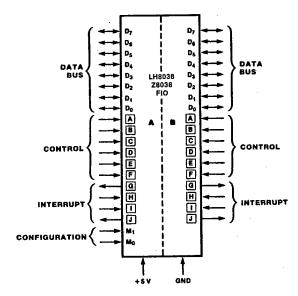

Figure 1. Pin Functions

Figure 2. Pin Assignments

67

| Pin<br>Assignments |            | Z-Bus<br>Low Byte | Z-Bus<br>High Byte | General<br>Purpose | Interlocked<br>HS Port* | IEEE 488<br>HS Port* |

|--------------------|------------|-------------------|--------------------|--------------------|-------------------------|----------------------|

| _                  | A          | REQ/WT            | REQ/WT             | REQ/WT             | RFD/ <del>DAV</del>     | RFD/DAV              |

|                    | Ē          | DMASTB            | DMASTB             | DACK               | ACKIN                   | FAV/DAC              |

|                    | B          | DS                | DS                 | RD                 | FULL                    | DAC/RFD              |

|                    | <b>D</b> . | R/W               | R/₩                | WŔ                 | EMPTY                   | EMPTY                |

| _                  | E          | CS                | <del>CS</del>      | . CS               | CLEAR                   | CLEAR                |

|                    | E          | ĀS                | <b>AS</b>          | C/D                | DATA DIR                | DATA DIR             |

|                    | G          | INTACK            | A <sub>0</sub>     | INTACK             | IN <sub>O</sub>         | IN <sub>0</sub>      |

|                    | H          | IEO               | A <sub>1</sub>     | IEO                | $OUT_1$                 | OUT                  |

|                    | H          | IEO               | ${\mathtt A}_2$    | IEI                | IN <sub>2</sub>         | IN <sub>2</sub>      |

|                    | 1          | INT               | A <sub>3</sub>     | ĪNT                | OUT <sub>3</sub>        | OUT <sub>3</sub>     |

<sup>\*</sup>B side only. See table below.

## **Description** (Continued)

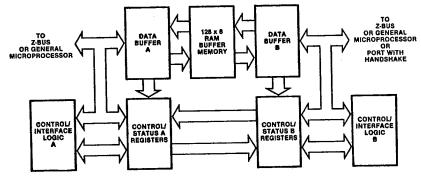

The internal functions of the Z-FIO are shown in the block diagram (Figure 3). It is made up of two sides that are identical except for programming. The side programmed by pins M<sub>0</sub> and M<sub>1</sub> is called the A side; the side programmed by bits  $SL_0$  and  $SL_1$  is called the B side. Common to both, and situated between the two sides, is the  $128 \times 8$  RAM used for data storage, two 7-bit counters, and various registers. The RAM is capable of simultaneous, independent read and write operations. This means, for example, that the A side CPU can write a byte of data into the FIO without disturbing a simultaneous read operation by the B side CPU. The outputs of the read and write counters are used to address the buffer RAM,

and also are fed into a subtractor to determine the current number of bytes in the memory. This number can be read by either CPU from a status register dedicated to each side. Another programmable register is compared against the status register to generate an interrupt and/or start and stop DMA transfers. A pair of port registers allows for communication between CPUs, bypassing the main buffer memory.

**Operating Modes.** The Z-FIO has twelve different programmable modes. (Table below.) The states of two package pins determine the mode of operation of the A side, and the B side is programmed by two bits (SL<sub>0</sub> and SL<sub>1</sub>) in one of the A side control registers.

Figure 3. Functional Block Diagram

| Operating<br>Modes | Mode | M <sub>1</sub> | M <sub>0</sub> | SL1 | SL <sub>0</sub> | A               | В               |

|--------------------|------|----------------|----------------|-----|-----------------|-----------------|-----------------|

|                    | 0    | 0              | 0              | 0   | 0               | Z-Bus Low Byte  | Z-Bus Low Byte  |

|                    | 1    | 0              | 0              | 0   | ı ·             | Z-Bus Low Byte  | General μP      |

|                    | 2    | ō              | 0              | 1   | 0               | Z-Bus Low Byte  | IEEE 488 HS     |

|                    | 3    | o              | 0              | 1   | 1               | Z-Bus Low Byte  | Interlocked HS  |

|                    | 4    | 0              | 1              | 0   | . 0             | Z-Bus High Byte | Z-Bus High Byte |

|                    | 5    | . 0            | ì              | 0   | 1               | Z-Bus High Byte | General #P      |

|                    | 6    | 0              | i              | 1   | 0               | Z-Bus High Byte | ieee 488 HS     |

|                    | . 7  | 0              | 1              | 1   | 1               | Z-Bus High Byte | Interlocked HS  |

|                    | 8    | ,              | 0              | 0   | 0               | General µP      | Z-Bus Low Byte  |

|                    | 9    | 1              | 0              | 0   | 1               | General µP      | General μP      |

|                    | 10   | 1              | 0              | ì   | Ō               | General µP      | IEEE 488 HS     |

|                    | 11   | 1              | 0              | 1   | 1               | General µP      | Interlocked HS  |

| Pins Common       | Pin                                                | Pin                                     | Pi                             | n          | Signal                                                                                                                                                    |  |  |  |  |

|-------------------|----------------------------------------------------|-----------------------------------------|--------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| To Both Sides     | Signals                                            | Names<br>M <sub>0</sub>                 | Numbers<br>21                  |            | Description                                                                                                                                               |  |  |  |  |

|                   | М <sub>О</sub><br>М <sub>1</sub>                   | M <sub>1</sub>                          | 19                             |            | M <sub>1</sub> and M <sub>0</sub> program Port 1<br>side CPU interface                                                                                    |  |  |  |  |

|                   | +5 Vdc                                             | +5 Vdc                                  | 40                             |            | DC power source                                                                                                                                           |  |  |  |  |

|                   | GND                                                | GND                                     | 20                             | )          | DC power ground                                                                                                                                           |  |  |  |  |

| Z-BUS<br>Low Byte | Pin                                                | Pin                                     | Pin Nu                         | et         | Signal<br>Description                                                                                                                                     |  |  |  |  |

| Mode              | AD <sub>0</sub> -AD <sub>7</sub>                   | Names<br>D <sub>0</sub> -D <sub>7</sub> | 11-18                          | 29-22      | Multiplexed bidirectional address/data lines, Z-BUS                                                                                                       |  |  |  |  |

|                   | (Address/Data) REQ/WAIT (Request/Wait)             | A                                       | 1                              | 39         | compatible.  Output, <u>active</u> Low, REQUEST (ready) line for DMA transfer; WAIT line (open-drain) output for synchronized CPU and FIO data transfers. |  |  |  |  |

|                   | DMASTB<br>(Direct Memory<br>Access Strobe)         | В                                       | 2                              | 38         | Input, active Low. Strobes DMA data to and from the FIFO buffer.                                                                                          |  |  |  |  |

|                   | DS<br>(Data Strobe)                                | C                                       | 3                              | 37         | Input, active Low. Provides timing for data transfer to or from FIO.                                                                                      |  |  |  |  |

|                   | R/W<br>(Read/Write)                                | D                                       | 4                              | 36         | Input; active High signals CPU read from FIO; active Low signals CPU write to FIO.                                                                        |  |  |  |  |

| •                 | CS<br>(Chip Select)                                | E                                       | 5                              | 35         | Input, active Low. Enables FIO. Latched on the rising edge of AS.                                                                                         |  |  |  |  |

|                   | ĀS<br>(Address Strobe)                             | F                                       | 6                              | 34         | Input, active Low. Addresses, $\overline{\text{CS}}$ and $\overline{\text{INTACK}}$ sampled while $\overline{\text{AS}}$ Low.                             |  |  |  |  |

|                   | INTACK<br>(Interrupt<br>Acknowledge)               | G                                       | 7                              | <b>3</b> 3 | Input, active Low. Acknowledges an interrupt.<br>Latched on the rising edge of AS.                                                                        |  |  |  |  |

|                   | IEO<br>(Interrupt<br>Enable Out)                   | Н                                       | 8                              | 32         | Output, active High. Sends interrupt enable to lower priority device IEI pin.                                                                             |  |  |  |  |

|                   | IEI<br>(Interrupt<br>Enable In)                    | I                                       | 9                              | 31         | Input, active High. Receives interrupt enable from higher priority device IEO signal.                                                                     |  |  |  |  |

|                   | INT<br>(Interrupt)                                 | 1                                       | 10                             | 30         | Output, open drain, active Low. Signals FIO interrupt request to CPU.                                                                                     |  |  |  |  |

| Z-BUS             |                                                    |                                         | Pin Numbers Pin Port Names 1 2 |            | Signal                                                                                                                                                    |  |  |  |  |

| High Byte<br>Mode | Pin<br>Signal <b>s</b>                             |                                         |                                |            | Description                                                                                                                                               |  |  |  |  |

| 1.1000            | AD <sub>0</sub> -AD <sub>7</sub><br>(Address/Data) | D <sub>0</sub> -D <sub>7</sub>          | 11-18                          | 29-22      | Multiplexed bidirectional address/data lines, Z-BUS compatible.                                                                                           |  |  |  |  |

|                   | REQ/WAIT<br>(Request/Wait)                         | A                                       | 1                              | 39         | Output, <u>active</u> Low, REQUEST (ready) line for DMA transfer; WAIT line (open-drain) output for synchronized CPU and FIO data transfers.              |  |  |  |  |

|                   | DMASTB<br>(Direct Memory<br>Access Strobe)         | В                                       | 2                              | 38         | Input, active Low. Strobes DMA data to and from the FIFO buffer.                                                                                          |  |  |  |  |

|                   | DS<br>(Data Strobe)                                | С                                       | 3                              | 37         | Input, active Low. Provides timing for transfer of data to or from FIO.                                                                                   |  |  |  |  |

|                   | R/ <del>W</del><br>(Read/Write)                    | D                                       | 4                              | 36         | Input, active High. Signals CPU read from FIO; active Low signals CPU write to FIO.                                                                       |  |  |  |  |

|                   | CS<br>(Chip Select)                                | E                                       | 5                              | 35         | Input, active Low. Enables FIO. Latched on the rising edge of AS.                                                                                         |  |  |  |  |

|                   | XC                                                 | F                                       |                                | 24         | Input active Low Addresses CS and INTACK are                                                                                                              |  |  |  |  |

34

33

32

31

30

7

8

9

10

G

Н

J

Signal/Pin Descriptions

Input, active Low. Addresses,  $\overline{\text{CS}}$  and  $\overline{\text{INTACK}}$  are sampled while  $\overline{\text{AS}}$  is Low.

Input, active High. With  ${\tt A}_1,\,{\tt A}_2,$  and  ${\tt A}_3,$  addresses FIO internal registers.

Input, active High. With  ${\tt A}_0,\,{\tt A}_2,\,{\tt and}\,\,{\tt A}_3,\,{\tt addresses}$  FIO internal registers.

Input, active High. With  $A_0$ ,  $A_1$ , and  $A_3$ , addresses FIO internal registers.

Input, active High. With  $A_0$ ,  $A_1$ , and  $A_2$ , addresses FIO internal registers.

AS (Address Strobe)

A<sub>0</sub> (Address Bit 0)

A<sub>1</sub> (Address Bit 1)

A<sub>2</sub> (Address Bit 2)

A<sub>3</sub> (Address Bit 3)

| Non-Z-BUS<br>Mode       | Pin<br>Signals                                | Pin<br>Names                   | Pin Nu<br>Po |            |                         | Signal<br>Description                                                                                                                                                                             |

|-------------------------|-----------------------------------------------|--------------------------------|--------------|------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | D <sub>0</sub> -D <sub>7</sub>                | D <sub>0</sub> -D <sub>7</sub> | 11-18        | 29-22      |                         | Bidirectional data bus.                                                                                                                                                                           |

|                         | (Data)<br>REQ/WT<br>(Request/Wait)            | A                              | 1            | 39         |                         | Output, <u>active</u> Low, REQUEST (ready) line for DMA transfer; WAIT line (open-drain) output for synchronized CPU and FIO data transfer.                                                       |

|                         | DACK<br>(DMA Acknowledge)                     | В                              | 2            | 38         |                         | Input, active Low. DMA acknowledge.                                                                                                                                                               |

|                         | RD<br>(Read)                                  | С                              | 3            | 37         |                         | Input, active Low. Signals CPU read from FIO.                                                                                                                                                     |

|                         | WR<br>(Write)                                 | D                              | 4            | 36         |                         | Input, active Low. Signals CPU write to FIO.                                                                                                                                                      |

|                         | CE<br>(Chip Select)                           | E                              | 5            | 35         |                         | Input, active Low. Used to select FIO.                                                                                                                                                            |

|                         | C/D<br>(Control/Data)                         | F                              | . 6          | 34         |                         | Input, active High. Identifies control byte on $D_0$ - $D_7$ ; active Low identifies data byte on $D_0$ - $D_7$ .                                                                                 |

|                         | INTACK<br>(Interrupt<br>Acknowledge)          | G                              | 7            | 33         | •                       | Input, active Low. Acknowledges an interrupt.                                                                                                                                                     |

|                         | IEO<br>(Interrupt<br>Enable Out)              | Н                              | 8            | 32         |                         | Output, active High. Sends interrupt enable to lower priority device IEI pin.                                                                                                                     |

|                         | IEI<br>(Interrupt<br>Enable In)               | I                              | 9            | 31         |                         | Input, active High. Receives interrupt enable from higher priority device IEO signal.                                                                                                             |

|                         | INT<br>(Interrupt)                            | 1                              | 10           | 30         |                         | Output, open drain, active Low. Signals FIO interrupt to CPU.                                                                                                                                     |

| Port 2-I/O<br>Port Mode | Pin<br>Signals                                | Pin<br>Names                   |              | in<br>bers | Mode                    | Signal<br>Description                                                                                                                                                                             |

|                         | D <sub>0</sub> -D <sub>7</sub><br>(Data)      | D <sub>0</sub> -D <sub>7</sub> | 29-22        |            | 2-Wire HS*<br>3-Wire HS | Bidirectional data bus.                                                                                                                                                                           |

|                         | RFD/DAV<br>(Ready for Data/Data<br>Available) | A                              | 39           |            | 2-Wire HS<br>3-Wire HS  | Output, RFD active High. Signals peripherals that FIC is ready to receive data. DAV active Low signals that FIO is ready to send data to peripherals.                                             |

|                         | ACKIN<br>(Acknowledge Input)                  | В                              | 38           |            | 2-Wire HS               | Input, active Low. Signals FIO that output data is received by peripherals or that input data is valid.                                                                                           |

|                         | DAV/DAC<br>(Data Available/Data<br>Accepted)  | В                              | 38           |            | 3-Wire HS               | Input; DAV (active Low) signals that data is valid on bus. DAC (active High) signals that output data is accepted by peripherals.                                                                 |

|                         | FULL                                          | С                              | 37           |            | 2-Wire HS               | Output, open drain, active High. Signals that FIO buffer is full.                                                                                                                                 |

|                         | DAC/RFD<br>(Data Accepted/Read<br>for Data)   | C<br>y                         | 37           |            | 3-Wire HS               | Direction controlled by internal programming. Both active High. DAC (an output) signals that FIO has received data from peripheral; RFD (an input) signals that the listeners are ready for data. |

|                         | EMPTY                                         | D                              | 36           |            | 2-Wire HS<br>3-Wire HS  | Output, open drain, active High. Signals that FIFO buffer is empty.                                                                                                                               |

|                         | CLEAR                                         | E                              | 35           |            | 2-Wire HS<br>3-Wire HS  | Programmable input or output, active Low. Clears all data from FIFO buffer.                                                                                                                       |

|                         | DATA DIR<br>(Data Direction)                  | F                              | 34           |            | 2-Wire HS<br>3-Wire HS  | Programmable input or output. Active High signals data input to Port 2; Low signals data output from Port 2.                                                                                      |

|                         | IN <sub>0</sub>                               | G                              | 33           | •          | 2-Wire HS<br>3-Wire HS  | Input line to $D_0$ of Control Register 3.                                                                                                                                                        |

|                         | OUT1                                          | Н                              | 32           |            | 2-Wire HS<br>3-Wire HS  | Output line from $D_1$ of Control Register 3.                                                                                                                                                     |

|                         | OE<br>(Output Enable)                         | I                              | 31.          |            | 2-Wire HS<br>3-Wire HS  | Input, active Low. When Low, enables bus drivers.<br>When High, floats bus drivers at high impedance.                                                                                             |

|                         | OUT <sub>3</sub>                              | J                              | 30           |            | 2-Wire HS               | Output line from D <sub>3</sub> of Control register 3.                                                                                                                                            |

<sup>\*</sup>Handshake

Signal/Pin Descriptions (Continued)